Benchmarking WSF & Original Boardsets

Background - Accurate or not ?

The question has come up several times about how accurate the WSF board

is compared to the original hardware. Also the comment that it's the

"closest" to the original. Well, the idea isn't to be

close, it's to be THE SAME.

So how to demonstrate this ?

Simple Benchmarking

The answer is a simple benchmark program that can be run on an original Revision D PCB, a Joust boardset, and on the WSF hardware. The code will exercise the features of the hardware and give some simple timing results.

- It waits for the top of a video frame

- Does a fast ROM to ram special chip block transfer ( blitter copy )

- Does two slow special chip block transfers ( 1/2 speed )

- Starts counting until the bottom of the frame is reached, each loop takes 10 CPU cycles to complete

- During this count the 4 millisecond interrupt occurs and the interrupt routine records the current count at the interrupt point. There are 4 of these interrupts per video frame.

- Displays the results Min/Max count and a running average of the last 256 counts

The minimum baseline is that the results MUST be the same between the boards.

This can only happen when :

- The special chip block transfers take the same number of cycles to complete

- The interrupts occurs at the same point in the overall count

- The timing loop for detecting bottom of frame completes at the

same point in time

Benchmarking Source

MC6809 source

for Benchmark - AS6809 Assembler formatted

Comparisons

The final numbers which are displayed in hex show how many of the 10 cycle loops could be completed in the remaining frame time after the special chip operations, also the interrupt processing takes up cycles too.

The goal here being to compare the results with the original hardware, the exact values returned are only valuable for comparison between the two boardsets.

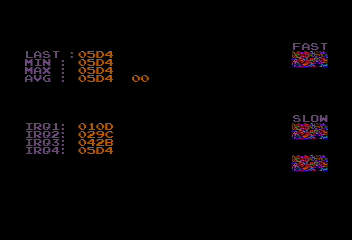

Original Boardset Benchmark Run

|

|

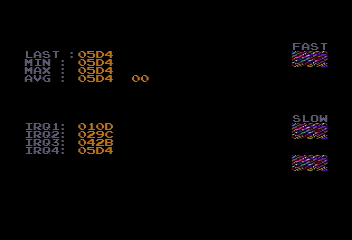

WSF v1.1 boardset

|

|

Results

The two video captures show the original revision D boardset run and the WSF 1.1

run with v1.10 FPGA and the benchmark code being located in place of the Robotron ROM.

The WSF board posts the exact same total results as the original, IRQ

counts are identical and the rolling average, once 256 counts are reached,

remains constant.

NOTE: Very Important - The data used for the transfer is basically random, so the blocks under fast and slow are different for each board test. What's important is the transfer speed, not the data.

|

|

Overkill ?

To be completely certain a 1048571 cycle capture

of the CPU executing the code on the original board and the FPGA hardware

was made using a Tektronix TLA 624 running in state capture.

This was used to verify the execution timing between the boards and ensure

they remained in lock-step. Below is a link to the highlights, two SC1

operations and the first interrupt. Also the end of the capture which

demonstrates the two CPUs are at exactly the same point in the code after

more than 1 million cycles and 1 second of execution. There's simply NO variance

between the two.

But some quick notes on the capture:

- Sampling was taken on the falling edge of the Q clock, so right in the middle of the 'E'

cycle

- The WMS cpu is fully buffered during special chip operations so the address and databus only

read hex 'FF'. With the WSF board the bus values can be seen during

the special chip 'blitter' operations.

- AVMA low cycles on the 6809 result in invalid data on the databus in the NEXT cycle. It's basically an unused bus cycle by the CPU and on the WSF board the ROM address 'FFFF' is still decoded.

MC6809 bus capture highlights - SC1 start, IRQ, state after 1 second

Final Summary

Then benchmark and bus capture demonstrate that the special chip timing and interrupts follow precisely the timings of the original boardset, there's simply NO variance between the two.

So in answer to the question "how close to original is it

?" I'm going to say "the same".